# Information Leakage Due to Cache and Processor Architectures

Zhenghong Wang

A DISSERTATION

PRESENTED TO THE FACULTY

OF PRINCETON UNIVERSITY

IN CANDIDACY FOR THE DEGREE

OF DOCTOR OF PHILOSOPHY

RECOMMENDED FOR ACCEPTANCE

BY THE DEPARTMENT OF

ELECTRICAL ENGINEERING

Advisor: Prof. Ruby B. Lee

November 2012

© Copyright by Zhenghong Wang, 2012.

All rights reserved.

## **Abstract**

When users share resources, interference between users often reflects their activities and thus leaks out information of a user to others. Microprocessors, and their associated cache memories, are typically one of the most shared resources in a computer system. Compared with traditional software-based and system-level information leakage channels, the ones in microprocessors are often much faster and more reliable – and hence more dangerous. They can also bypass existing software-based protection and isolation mechanisms, and can nullify any confidentiality or integrity protections provided by strong cryptography. Because of the ubiquitous deployment of microprocessors and the fact that the attacks are effective on essentially all modern processors, such microprocessor-level information leakage exists in almost all computing systems and has become a serious security threat to a wide spectrum of platforms and users.

Motivated by the increasing importance of the processor and cache information leakage problem, this dissertation aims to investigate the information leakage problem in microprocessors in a more generalized manner. The goal is to first understand the fundamental, rather than attack-specific, mechanisms that enable information leakage, and then propose countermeasures that attack the root causes and thus are generally effective. The dissertation also attempts to develop a theoretical model of information leakage channels, which can help analyze existing channels, identify new channels, evaluate their severity, and avoid such channels in future designs.

The dissertation starts with concrete practical issues that are of high importance. It first analyzes the recent cache-based software side-channel attacks, revealing their common root cause, then proposing novel cache designs that can effectively defend against all attacks in this category without compromising performance, power efficiency and cost. The proposed Newcache design can even improve performance over traditional cache architectures. The dissertation also analyzes existing processor architectures, identifies several new covert channels that are much faster than traditional channels, and discusses alternative countermeasures. The dissertation then generalizes the problem of covert channels with abstract modeling and analysis, which clarify the ambiguity in traditional classifications of covert storage versus timing channels, help identify new channels and reveal limitations of existing covert channel identification methods. The dissertation also recognizes that asynchronism is an inherent characteristic of covert channels that should be properly captured in channel capacity estimation. Quantitative results are presented.

# Acknowledgements

It would not have been possible to write this doctoral dissertation without the help and support from many people. There are no words adequate to express my deep gratitude to all of them.

First of all, I would like to thank my thesis advisor, Professor Ruby Lee, for the patient guidance, constant encouragement and insightful advice she has provided throughout my time as her student. During the hard times in my thesis writing, in particular after I had started a fast-paced job in Silicon Valley and fathered two children, it was her patience and persistence that drove me to get through all the difficulties and keep making progress. I truly enjoyed working with her and feel lucky for being one of her students.

I am grateful to Professor Andrew Appel and Professor Mung Chiang for taking time to read the thesis as well as providing invaluable feedback and suggestions that help clarify the work. I also thank the faculty and staff of the Princeton University Department of Electrical Engineering for all the help and advice they gave me during my study in Princeton.

I thank the members of the PALMS group for their direct and indirect help in improving the work. I enjoyed the fun and inspiring discussions with them. I also thank all my friends, who helped make my life and study in Princeton more enjoyable.

Finally, I would like to thank my family. My wife Yan has provided endless support in all aspects of my life. My lovely son Eddie and daughter Eileen came to this world just in time to make my thesis writing more challenging. They however bring great happiness and helped me truly understand the meaning of the word "cherish". My parents and sisters have always cared for me, loved me, and supported me, even when they are thousands of miles away. To them I dedicate this thesis.

# Contents

| Αł | ostrac            | et                                                                                                                                                               | iii                            |

|----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Α  | cknov             | wledgements                                                                                                                                                      | iv                             |

| Co | onten             | ts                                                                                                                                                               | V                              |

| Li | st of             | Figures                                                                                                                                                          | vii                            |

| Li | st of             | Tables                                                                                                                                                           | ix                             |

| 1  | 1.1<br>1.2        | oduction Information Leakage: Practical and Theoretical Issues New Issues due to Processor Architectural Features Dissertation Overview                          | 1<br>1<br>3<br>6               |

| 2  | 2.1<br>2.2        | ated Work Covert Channels Side Channel Attacks Information Hiding Miscellaneous Unintended Data Exposure Scope of this Dissertation                              | 8<br>8<br>16<br>24<br>27<br>28 |

| 3  | 3.1<br>3.2        | he-based Side Channel Attacks: Analysis and Countermeasures<br>Overview<br>Attack Analysis<br>New Cache Designs for Mitigating Software Cache Attacks<br>Summary | 29<br>29<br>30<br>37<br>52     |

| 4  | 4.1<br>4.2<br>4.3 | Overview The Proposed Cache Architecture Analyses and Evaluations Additional Benefits                                                                            | 53<br>53<br>53<br>64           |

|   | 4.5                                     | Summary                                             | 70  |

|---|-----------------------------------------|-----------------------------------------------------|-----|

|   | App                                     | endix 4                                             | 71  |

| 5 | Fas                                     | t Covert Channels in Microprocessors                | 74  |

|   | 5.1                                     | Introduction                                        | 74  |

|   | 5.2                                     | SMT-based Covert Channels                           | 74  |

|   | 5.3                                     | Covert Channels due to Control Speculation in IA-64 | 80  |

|   | 5.4                                     | Remarks                                             | 85  |

|   | 5.5                                     | Summary                                             | 86  |

| 6 | On Covert Channel Modeling and Analysis |                                                     | 88  |

|   | 6.1                                     | Introduction                                        | 88  |

|   | 6.2                                     | Storage Channel and Timing Channel Revisited        | 89  |

|   | 6.3                                     | Capacity Estimation of Asynchronous Covert Channels | 96  |

|   | 6.4                                     | Summary                                             | 103 |

| 7 | Conclusions                             |                                                     | 105 |

|   | 7.1                                     | Contributions                                       | 106 |

|   | 7.2                                     | Future Work                                         | 107 |

| R | efere                                   | nces                                                | 109 |

# List of Figures

| Figure 1-1  | An input-dependent loop                                             | 4  |

|-------------|---------------------------------------------------------------------|----|

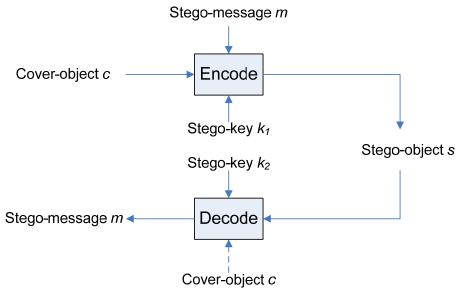

| Figure 2-1  | A generic process of message embedding and retrieving               | 25 |

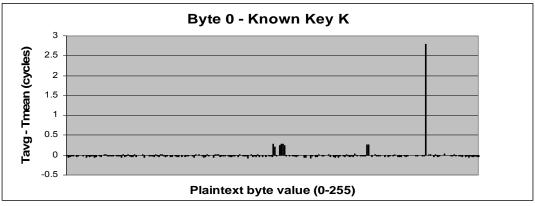

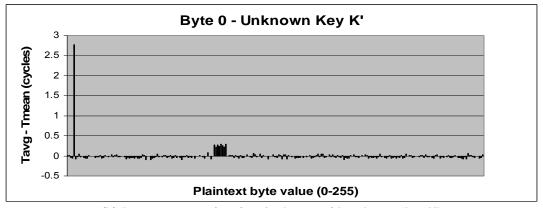

| Figure 3-1  | (a)Timing characteristic generation (b)Key-byte searching algorithm | 31 |

| Figure 3-2  | Timing characteristic charts for byte 0                             | 32 |

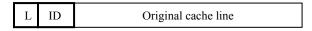

| Figure 3-3  | A cache line of the PLcache                                         | 38 |

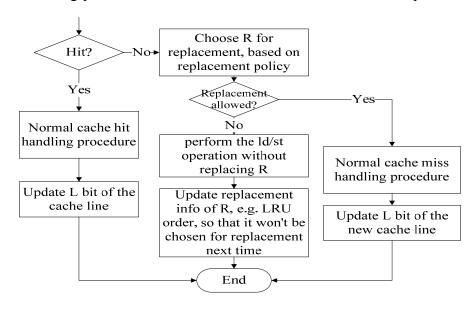

| Figure 3-4  | Cache access handling procedure for PLcache                         | 39 |

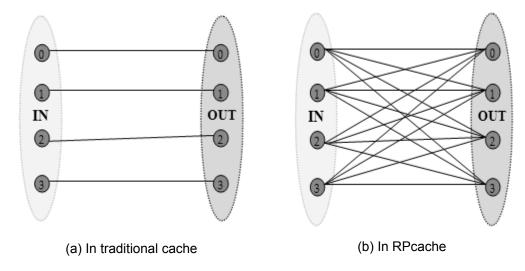

| Figure 3-5  | A logical view of the RPcache                                       | 42 |

| Figure 3-6  | Cache access handling procedure for RPcache                         | 44 |

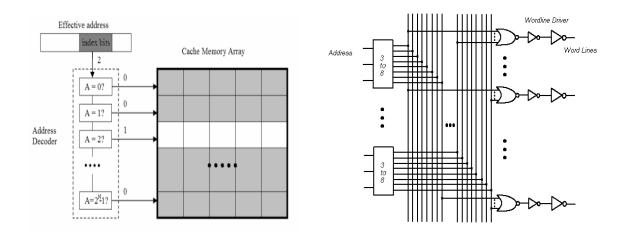

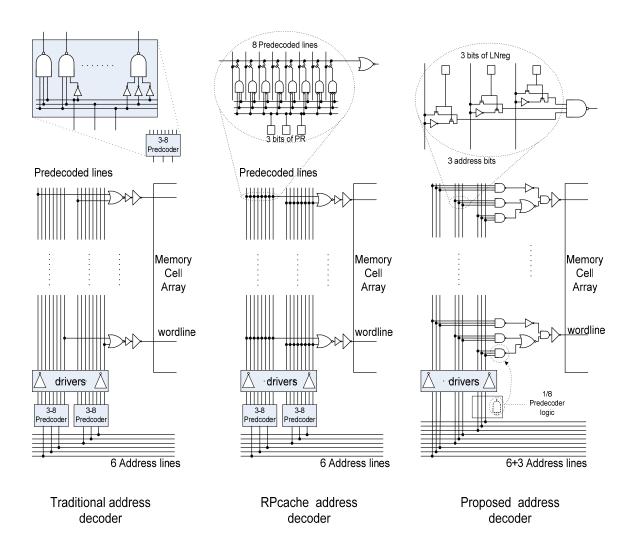

| Figure 3-7  | Address decoder circuitry of the RPcache                            | 45 |

| Figure 3-8  | A channel model of the cache-address-based side channel             | 47 |

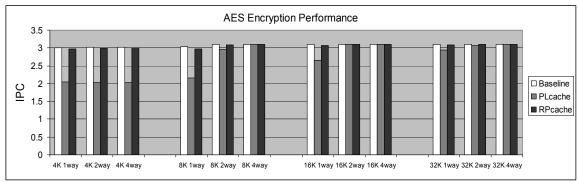

| Figure 3-9  | Performance comparison of AES code                                  | 50 |

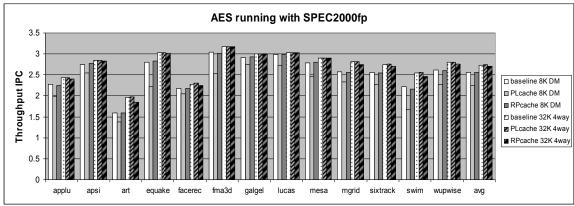

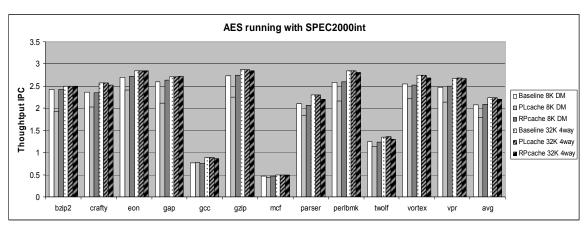

| Figure 3-10 | Performance impact on overall throughput                            | 50 |

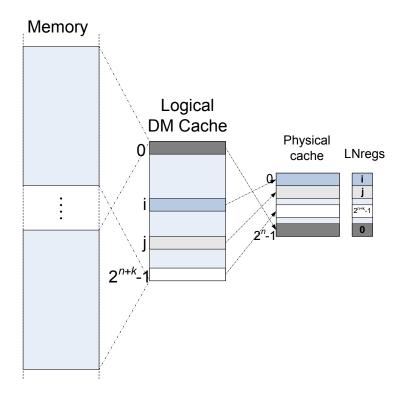

| Figure 4-1  | Mapping memory space to the physical cache                          | 54 |

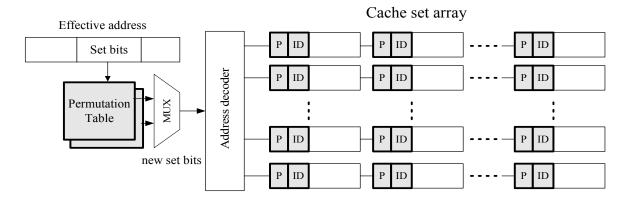

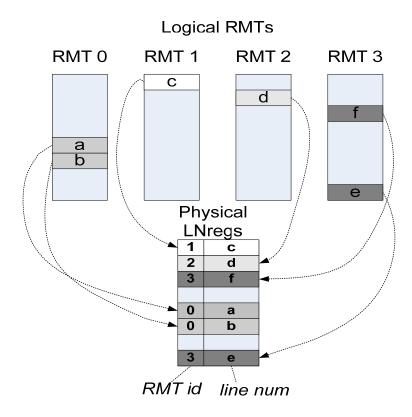

| Figure 4-2  | Supporting multiple logical RMTs                                    | 55 |

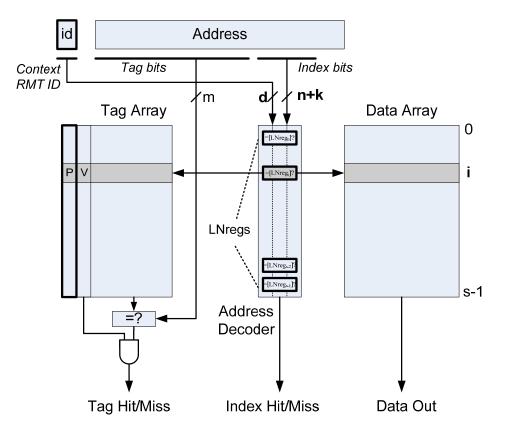

| Figure 4-3  | The proposed cache architecture                                     | 56 |

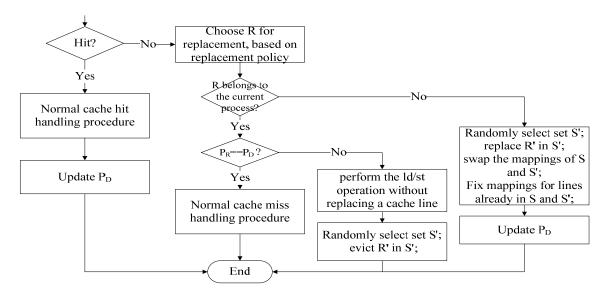

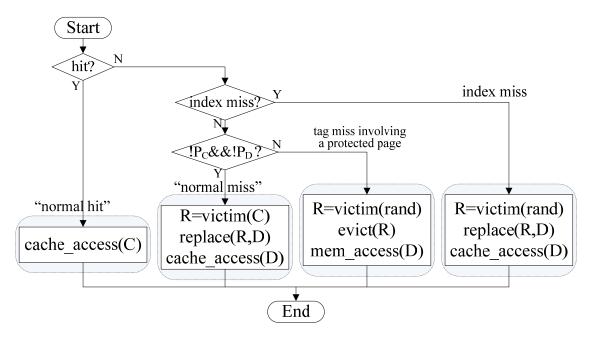

| Figure 4-4  | New security-aware random cache replacement algorithm               | 57 |

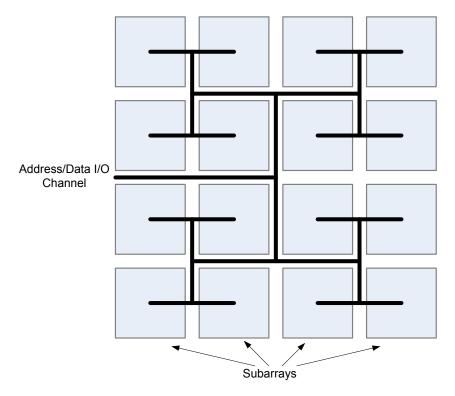

| Figure 4-5  | A generic cache organization                                        | 59 |

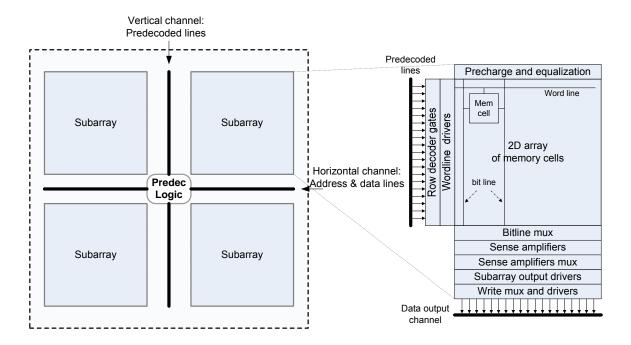

| Figure 4-6  | Address decoder and subarray structures                             | 60 |

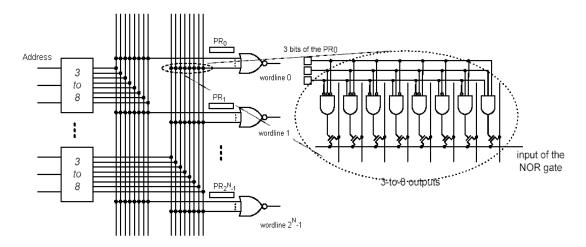

| Figure 4-7  | (a)logical view of the address decoder (b)physical implementation   | 61 |

| Figure 4-8  | Overall structures of the address decoders                          | 62 |

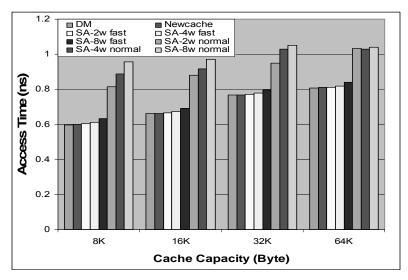

| Figure 4-9  | Cache access time comparison                                        | 64 |

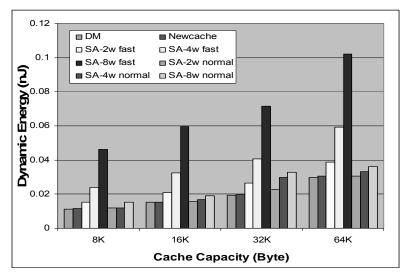

| Figure 4-10 | Dynamic read energy                                                 | 64 |

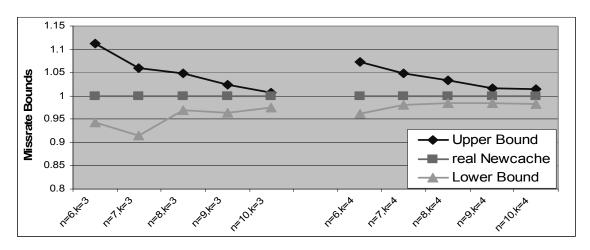

| Figure 4-11 | Accuracy of the miss rate bounds                                    | 66 |

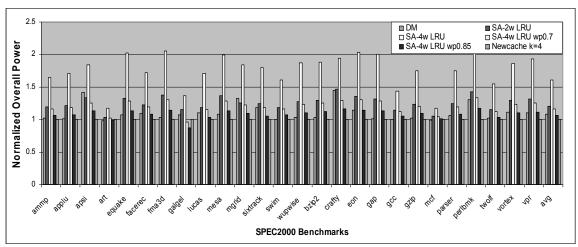

| Figure 4-12 | Comparison of the overall power consumption                         | 68 |

| Figure 5-1  | Pseudo code for SMT/FU channel                                      | 76 |

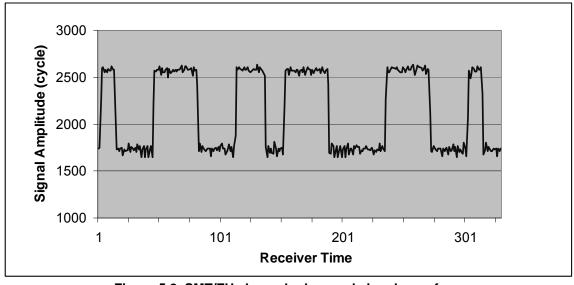

| Figure 5-2  | SMT/FU channel: observed signal waveform                            | 76 |

| Figure 5-3  | Implementation code of MULTIPLY(), NULL() and RUN()                 | 78 |

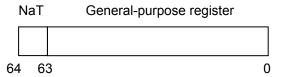

| Figure 5-4  | 65-bit general-purpose register in IA-64                            | 81 |

| Figure 5-5  | Sample code for IA-64 control speculation                           | 81 |

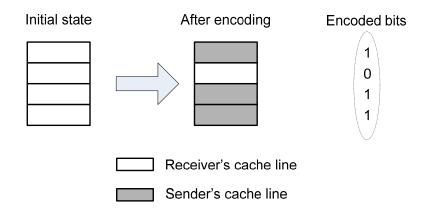

| Figure 5-6  | Encoding in L3 cache                                                | 82 |

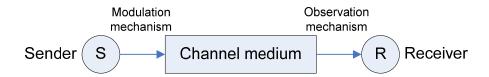

| Figure 6-1  | An abstract channel model for information leakage                   | 90 |

| Figure 6-2  | Spatially encoding four bits into a four-entry direct mapped cache  | 91 |

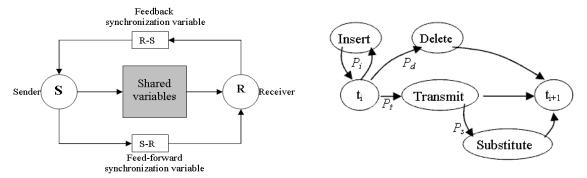

| Figure 6-3  | A synchronization mechanism using two variables                     | 98 |

|             |                                                                     |    |

| Figure 6-4 | Insertion-deletion channel                                        | 98  |

|------------|-------------------------------------------------------------------|-----|

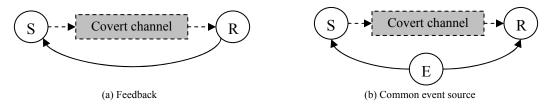

| Figure 6-5 | Two fundamental synchronization methods                           | 99  |

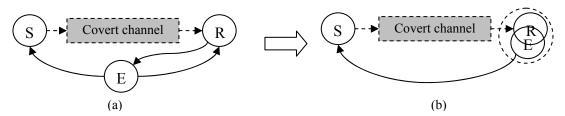

| Figure 6-6 | Using common events won't get better capacity than using feedback | 102 |

# List of Tables

| Table 3-1 | Optional ISA extension for PLcache             | 39 |

|-----------|------------------------------------------------|----|

| Table 3-2 | Potential API calls for PLcache                | 39 |

| Table 3-3 | Timing and power estimation of RPcache         | 46 |

| Table 3-4 | Simulation parameters                          | 49 |

| Table 3-5 | Comparing with prior-art partitioned cache     | 51 |

| Table 4-1 | Definitions and notations                      | 58 |

| Table 4-2 | HSPICE results on address decoder delay        | 65 |

| Table 4-3 | Miss rate comparison                           | 67 |

| Table 4-4 | Caches considered                              | 71 |

| Table 5-1 | Information rate comparison of covert channels | 85 |

# Chapter 1

# Introduction

The term "information security" is often interpreted as the protection of information and information systems from unauthorized access, use, disclosure, disruption, modification, or destruction. The basis of information security consists of three components: confidentiality, integrity and availability. Confidentiality is the concealment of information, ensuring that information is accessible only to authorized parties. Integrity means guarding improper or unauthorized information modification or destruction. Integrity includes data integrity – the content of the data, and also origin integrity – the source of the data. Availability is the access to, and use of, information and resources in a timely and reliable manner.

Information leakage is a direct threat to confidentiality. It leads to the disclosure of information to someone who should not learn the information. In many situations, the leaked information may not be the ultimate target of an attack. It may help compromise integrity or availability as well and facilitate further steps of the attack, e.g., gaining higher privilege or even taking over the whole system. In practice, despite huge efforts in securing computer systems, the information leakage problem exists, more or less, in almost all practical systems.

### 1.1 Information Leakage: Practical and Theoretical Issues

Many factors contribute to the wide existence of the information leakage problem – some are due to practical reasons whereas others lie in the fundamental theory upon which the systems are built.

Among the practical issues, design flaws and implementation errors are common causes of information leakage problems. Design flaws may be introduced at various levels in the development phase. At the system level, incorrect assumptions and/or an insufficient threat model often lead to bad design decisions and flawed system architecture. A good example is the first generation XBOX gaming console. Among many mistakes that Microsoft made [1] (from the hackers' perspective), transmitting the

secret key in plaintext over the HyperTransport bus between the CPU chip and the Southbridge chip<sup>1</sup>, which is directly visible to the hackers, is the worst one. The rationale behind this design decision was probably the fact that the HyperTransport bus was so fast that no logic analyzer at that time could sniff the bus, and it is a cheaper design. But it turned out to be an underestimation of the hackers' resources and expertise. Custom hardware was quickly developed and the attack succeeded [1].

When getting into low level implementations, the chances of developers making mistakes become higher due to the increasing amount of details involved. In complicated system design that involves developers with various skill levels producing millions of lines of code, having errors in implementation is essentially inevitable.

The common use of less secure programming languages, e.g., C, has also contributed to many of the implementation bugs. Unlike other high-level programming languages like Java, they are more vulnerable to security issues like the buffer overrun problem [2-3], which has been recognized as a major threat to software/system security. In reality, not all these errors can lead to information leakage, but many of them do cause issues, e.g., the well known "kernel memory disclosure" problem, which exposes the content of kernel memory to unprivileged users [4].

In addition to the mistakes made in the design and development stage, information leakage problems can also be introduced in the later stages of the system life cycle, e.g., after the system is placed online, or even after the life of the system has ended. Security problems in live systems are often due to incorrect configurations and/or bad practices in system management and maintenance, e.g., inappropriate security policies for users and data objects or simply bad passwords. There can also be problems after a system or some of its components are dead. Sensitive information should be securely shredded or carefully scrubbed, or it has to be properly protected or migrated to other live systems. Dead components, particularly storage devices, should be carefully processed before they leave the trusted sites. It is not difficult for an attacker to recover data from a dead hard drive. Advanced technology can even recover data from a hard drive that has been overwritten with 0's [5].

Theoretically, all these practical issues can be avoided, given sufficient time, effort and resources. However, there are some types of information leakage, which lie in the fundamental theoretic model on which systems are built, that are unavoidable even with perfect design, implementation, configuration and maintenance.

One theoretical issue originates from the process of abstraction, in which the physical system is abstracted into a logical model, which preserves only the properties of interest and discards the rest. In reality this is a very common practice as it allows most of the development efforts to be independent of physical devices. However, any protection mechanisms developed upon the logical system model would be effective only for the aspects that are modeled. Information may still leak out via the physical aspects that are not modeled in the system, e.g., through acoustic or electro-magnetic emission, power variation, or even thermal activities. Attacks based on these issues are often referred to as *side channel attacks*. One may argue that if the system model includes all aspects of the physical system, the design may be immune to side channel attacks. However, that would only be possible for very simple devices, assuming it is possible to enumerate all physical

2

<sup>&</sup>lt;sup>1</sup> The Southbridge is one of the two chips in the chipset on a PC motherboard. It typically handles the I/O devices such as USB, audio, ISA bus, PCI, IDE channels etc.

properties. For most practical systems, it is infeasible to consider all physical aspects of the system in the design and implementation.

Another example of a theoretical issue relates to covert channels, which are often referred to as channels that are neither designed nor intended to transfer information [6]. One type of covert channels, the covert *storage* channels, make use of entities not normally viewed as data objects to transfer information from one process to another. Another type of covert channels, the covert *timing* channels, exploit the temporal characteristics of events to transfer information. As an example of a covert storage channel, the file lock attribute can be used to transfer information. One process can lock a file to encode a bit '1' and unlock the file to encode a bit '0', and another process can retrieve the bit by checking if the file is locked. As an example of a covert timing channel, information can be leaked out by modulating the use of CPU time, e.g., a process can try to use as much CPU time as possible to indicate a bit '1', and try not to use any CPU time to indicate a bit '0'. Other processes can extract the information by observing the system response time.

Due to the essentially unlimited number of ways in exploiting various objects and resources in a system, covert channels widely exist in practically all computer systems. Despite extensive work on covert channel analysis, systematic identification and elimination of covert channels remains a very difficult problem.

#### 1.2 New Issues due to Cache and Processor Architectural Features

In the literature, information leakage problems were mostly studied in the area of covert channels and side channels which focused on either specific hardware/software targets such as cryptographic devices and software ciphers, or system and software level covert channel issues. Information leakage due to hardware processors (including their tightly coupled caches) did not receive as much attention in the past.

Compared with information leakage at other levels of a system, information leakage at the processor level is unique in several aspects. First, as the central processing unit of a system, processors are typically the most shared resources in the system – often among all users who may belong to different security domains, and therefore is an ideal place for inferring information from interference between users. Second, microprocessors are fast, and covert or side channels based on processor level interferences can often be orders of magnitude faster than those at the software level. Third, the processor level sharing often breaks software level isolation mechanisms like virtual machines (VMs). For example, two logically isolated VMs can still be running on the same physical microprocessor and share caches. It has been demonstrated in several recent work that sensitive information like cryptographic keys can be leaked out through shared caches. Fourth, in a processor the clocks are usually derived from common oscillating sources. This makes synchronization easier, e.g., between sender and receiver in covert channels, and therefore leads to faster covert channels.

The situation is getting even worse over the last few decades. The advances in process technology have enabled billions of transistors to be integrated into a single chip, allowing more on-chip resources to be allocated for new architectural and microarchitectural features that enhance performance, power efficiency, etc. Such new

```

...

/* loop counter is dependent on program input */

int cnt;

cnt = input();

for i = 0 to cnt do begin

...; /* some work done here */

end;

...

```

Figure 1-1. An input-dependent loop

additions however were often designed without being carefully examined for security. Furthermore, the increased system complexity increases the difficulty of identifying and mitigating of information leakage channels.

To understand the information leakage problem in processors, we first need to know what information can be leaked out, by what means. A program running on a processor may leak information due to various reasons, some dependent on processor features while others not. Information leakage due to a program's inherent characteristics, e.g., its algorithmic computation complexity, is often independent of the type of processor on which the program is running. Figure 1-1 is a simple example of this. Since the number of iterations is determined by the program input, the execution time of this code segment would reveal the value of the input (whether it is small or large), no matter what type of processor it runs on.

On the other hand, other types of information leakage by a program may depend on what processor it is running on. For example, a program doing table lookups may have constant execution time if the table lookups take constant time. This may be true if the program runs on a processor without caches and the memory accesses take constant time. However, if the underlying processor has a cache, constant table lookup time may not be possible. A table lookup that hits in the cache would take shorter time than one that misses in the cache. In this dissertation, we focus on such information leakage that is specifically caused by cache and processor architectural features.

#### 1.2.1 Information Sources in Processors

Despite various forms of information leakage and the resulting attacks, in this dissertation they are categorized into two types, as we will explain below. Most modern processors (if not all) are based on the stored-program architecture, which consists of a processing unit, that performs operations to manipulate data, and memory storage, that keeps instructions as well as data. The instruction memory and the data memory can be unified, e.g., in Von Neumann Architecture, or separated, e.g., in Harvard Architecture. Programs running on such architectures involve two types of operations: fetching and storing the instructions or data, and processing the instructions or data. The first type of operations deal with the object location information, and the second type of operations deal with the values of the objects. These two types of information – the object location and the object value – are the main sources of information leakage in processors.

According to the type of operations that a processing unit is involved in, most components in real processors can be categorized into two classes. Components such as the instruction decoder and functional units such as ALUs are units that manipulate or transform object values. Components such as caches, TLBs, and branch predictors perform or facilitate object fetching and/or storing operations and process information about the object locations. During the operations of such components, information about the operations being performed can often be leaked out, which is the basis of real information leakage attacks. In the next section, basic mechanisms of information leakage will be summarized and examples given.

#### 1.2.2 Basic Leakage Mechanisms

Information leakage mechanisms in processors mostly fall into two categories. The first type of leakage occurs during the operation of the information-leaking component. For example, the branching unit may exhibit different power consumption characteristics, indicating a taken branch or a non-taken branch. Another example is the memory system. When performing a memory access operation, the memory system may exhibit input-dependent delay – due to cache hit or miss, and can leak information about the input, i.e., the address of the access. Since such information leakage is due to the use of on-chip resources, we refer to this type of leakage as *leakage by resource use*.

Another type of information leakage is due to reporting mechanisms that exist in many modern processors. For the purpose of debugging and performance analysis and tuning, modern processors often implement event monitors and counters accessible to system software as well as application software. Such reporting mechanisms allow a program to learn information about other programs that it may not be able to observe via the first type of information leakage. We refer to this type of information leakage as *leakage by event reporting*. Note that leakage by event reporting does not require direct use of resources.

#### Leakage by resource use

Based on what type of information is leaked, leakage by resource use can be value-dependent leakage, address-dependent leakage, or hybrid leakage.

Value-dependent leakage: If a processing unit exhibits input-dependent behavior, it may leak out information about the value of the object being processed, causing value-dependent leakage. For example, functional units may exhibit input-dependent power consumption and leak out information about the input value, e.g., its hamming weight. Some simple CISC processors may implement complex instructions with micro programs, which could lead to variable execution cycles and leak information about the value of the instruction operand.

**Address-dependent leakage:** If a processor component operates on an object's location information, i.e., its address, it may cause address-dependent leakage. The branching unit and memory system including caches, Translation Lookaside Buffers (TLBs), etc., are good examples of this. A prefetching unit may also exhibit different behaviors for different access patterns, leaking out information about the memory access history.

**Hybrid leakage**: The leakage of object values and location information can sometimes be twisted together. For example, value prediction [7-8] and speculative execution [9]

may speculate on operand values and lead to different execution paths for correct and incorrect prediction or speculation, respectively. The leakage of object values in such mechanisms, however, is through the variations of the objects' addresses.

#### Leakage by event reporting

Unlike leakage by resource use, leakage by event reporting usually does not involve operations that generate information-leaking variations of object values or locations. Instead, it exposes events that are already generated. For example, the performance counters in Intel processors can record information about a wide range of events including the number of cache misses, or retired branches, or TLB references, or microoperations (uops) of various types, etc. In addition to the dedicated reporting mechanisms, other processor architectural features may also expose events that are originally invisible to a program. For example, control speculation in IA-64 allows a program to see the occurrence of an individual event such as a cache miss with a long delay, a page fault, an access right violation, etc.

Due to the different nature of the two types of information leakage mechanisms, the leaked information has different characteristics. Leakage by resource use usually exposes primitive information of individual operations, e.g., values or locations of certain objects, whereas leakage by event reporting usually exposes composite "high" level events that represent the overall program behavior. Leakage by resource use therefore is commonly exploited in attacks that require accurate knowledge of certain internal objects of a program, e.g., side channel attacks, whereas leakage by event reporting is more suitable for constructing covert channels – it provides a large set of mechanisms that allow the receiver of the channel to observe various aspects of the behavior of the sender, which is ideal for covert channels.

#### 1.3 Dissertation Overview

Despite the extensive research in the areas of covert channels and side channel attacks, the information leakage problem due to microprocessors did not receive as much attention in the past. Existing work include the information leakage through the memory bus, covert timing channels based on CPU or bus contention, and cache based covert channels and side channel attacks, etc. We review all this in detail in chapter 2. All these work however addressed only specific attacks and the coverage is very limited. To the best knowledge of the author, a comprehensive and systematic examination of information leakage at the processor architectural level is not available.

This work is motivated by the fact that there are rich and unique mechanisms in microprocessors which allow unintended and undesired information leakage, and the lack of a thorough investigation of the problem in the past. It aims to analyze and understand information leakage at processor architectural and micro-architectural level, and research suitable countermeasures before irreparable damage is done. The work first investigates real attacks, especially on processor caches, that are of high significance, analyzes concrete problems and proposes novel and effective solutions. The work then generalizes the problem with abstract modeling and classification, based on which theoretical analyses are performed. The generalized discussion helps clarify past misconceptions and

allows better modeling and clearer classification of information leakage channels. The better understanding of the nature of the problem also helps identify new information leakage channels.

The rest of the dissertation is organized as follows. In chapter 2 we review related past work, including covert channel analysis, side channel attacks, steganography as well as other information hiding techniques. In chapters 3, 4, and 5, concrete information leakage problems of significant importance are first addressed. Chapter 3 [10] analyzes the recently reported cache based side channel attacks and reveals the common root cause of these attacks. Novel cache architectures, including the PLcache and RPcache, are then proposed as universal countermeasures to such classes of attacks. In chapter 4 [11], we present Newcache, another novel cache architecture that improves performance even as it improves security. The proposed cache architecture inherits the short access time and high power efficiency from the direct mapped cache architecture, and at the same time, enjoys low miss rates comparable to a highly associative cache. It also can prevent information leakage in caches and hence is immune to the cache-based side-channel attacks. In addition, it can bring several other benefits such as fault tolerance, power and thermal optimizations. In chapter 5 [12], we present new fast covert channels we identified in processors, and propose corresponding countermeasures. The theoretical aspect of the information leakage problem is addressed in chapter 6 [13-14]. As the basis of further theoretical analysis, the information leakage mechanisms are first generalized and an abstract channel model is constructed. The ambiguity in traditional classifications of covert storage and timing channels is explained and we propose a new classification that resolves this ambiguity. This chapter also presents new results on channel capacity estimation, pointing out that asynchronism is an inherent characteristic of covert channels that should be properly captured in channel capacity estimation. Finally, Chapter 7 summarizes the contributions of the work and discusses possible directions of future work.

# Chapter 2

# Related Work

In the most general sense, information leakage can be defined as any unwanted information distribution or transfer. It may occur anywhere in a system and the information can be leaked out in vastly different ways. In practice, information leakage is often a result of access control failure, which leads to direct exposure of information to unauthorized parties. Information can also be leaked out indirectly, even when the system has properly designed and implemented access control. In a computer system, the operations that process data can cause interference observable to others, from which certain information of the data being processed can be inferred. Many covert channels and side channel attacks are based on such indirect information leakage. Information leakage may occur at various levels of the system. For example, application software may fail to properly clear cryptographic keys after use, system software may contain bugs that allow exposure of kernel memory to unprivileged processes, and hardware circuits may exhibit data dependent behaviors such as various power consumption or operation timing. Information leakage can be unintended leakage, e.g., due to buggy software that accidentally expose one's private data to others. Information can also be leaked out intentionally, e.g., by a Trojan horse that deliberately sends out information. Due to the abundance of information leakage mechanisms, information leakage was studied in a wide range of research areas in the literature, each of which investigates certain aspects of the problem in a particular context. In this section, the related work including covert channels, side channel attacks, information hiding and miscellaneous unintended data exposure are first reviewed. The relationship between the main focus of this work and the past work is then summarized, and the scope of this dissertation clarified.

#### 2.1 Covert Channels

#### 2.1.1 Definitions of Covert Channels

In the literature, the term "covert channel" was used to refer to a variety of unconventional communication mechanisms. This section gives an overview of covert channels, reviews the existing definitions, and clarifies the subject of discussion.

The notion of covert channels was first introduced by Lampson [6]. He examined nontraditional means of information transfer, which he referred to as "covert channels", in the context of program confinement. In such a context, there are normally two parties (e.g., processes in a computer system) involved in a covert channel: the sender S and the receiver R, who are disallowed by the system security policy to communicate in one or both directions between them. S and R therefore have to retort to nontraditional ways to exchange information. Lampson's definition of covert channels was [6]:

Definition 1: channels that are neither designed nor intended to transfer information.

This definition points out the nature of covert channels but does not provide information on how covert channels can be constructed. Definitions 2 and 3 define covert channels from an implementation perspective.

Definition 2: channels that use entities not normally viewed as data objects to transfer information from one subject to another [15].

Definition 3: channels that are a result of resource allocation policies and resource management implementation [16].

Unlike in normal communication channels, information transferred in covert channels is usually encoded into objects not used for data storage (e.g., control objects rather than files or messages), or modulated over the use of shared resources, causing interference among processes from which information can be indirectly inferred. Below are two examples of such covert channels:

#### **Example 1: the file lock channel [17]**

In systems that provide file locking capability, the status of the file lock can be exploited to transfer information between processes. The sending process S can lock a file to indicate a 1 and unlock it to indicate a 0. The receiving process R can then extract the bit by checking the status of the lock.

The file lock channel is a representative example of covert channels under Definition 2. There are also other means to construct covert channels, among which exploiting shared resources, e.g., the CPU time, is the most common one.

#### **Example 2: the CPU scheduling channel**

In multi-tasking systems, the CPU is shared among multiple processes, each of which is given a certain amount of CPU time. A process can modulate information over its own use of CPU time and interfere with other processes. For example, the sender S can use as much CPU time as possible to indicate a 1 and use little CPU time to indicate a 0. The receiver R can recover the information by comparing its own progress with a timer. A slow down of R's execution would indicate a bit 1 sent by S.

Definitions 2 and 3 however can hardly cover all covert channels due to the unlimited number of ways that covert channels can be constructed with. For example, Definition 2 did not consider the covert channels based on the timing of events. Furthermore, although all the previous definitions are intuitively clear, they are informal and ambiguous, and

thus can hardly be used in systematic covert channel analysis with automatic tools. In [17-18], security policy was introduced into the definition of covert channels, which removes much of the ambiguity.

Definition 4: channels that allows a process to transfer information in a manner that violates the system's security policy [18].

Definition 5: given a nondiscretionary (e.g., mandatory) security policy model M and its interpretation I(M) in an operating system, any potential communication between two subjects  $I(S_h)$  and  $I(S_i)$  of I(M) is covert if and only if any communication between the corresponding subjects  $S_h$  and  $S_i$  of the model M is illegal in M [17, 19].

In particular, Definition 5 pointed out the irrelevance of covert channels with discretionary security policies [17]. Implementations of discretionary policy models within operating systems cannot determine whether a program may release information in a legitimate manner [20], hence any user can make use of the legitimate communication channels rather than covert channels to leak out information. Compared with exploiting mechanisms not intended for communications as in covert channels, leaking information through legitimate channels is much faster, more convenient and harder to detect, in particular with the help of steganography as well as other data hiding techniques.

Definitions 4 and 5 are particularly interesting in the context of Multi-Level Security (MLS) systems where mandatory security policies are widely used and formally defined. DoD's Trusted Computer System Evaluation Criteria (TCSEC) [18] has adopted such a definition. In this dissertation, a combination of Definitions 1 and 5 is adopted as the definition of covert channels. This is not to create a new definition, but to clarify the three characteristics of covert channels. More specifically, by "covert channel" we refer to a channel that:

- 1. exploits mechanisms that are not designed for communications,

- 2. violates the system's security policy M, where M is a non-discretionary policy,

- 3. involves an insider that intentionally sends out information.

Note that the third characteristic was not explicitly stated in definitions 1 to 5, but was indeed assumed in the context of discussion, e.g., insider attacks in MLS systems. This distinguishes covert channels from other unintentional information leakage problems.

In addition to the covert channels defined above, there are also other uses of the term "covert channels" in the literature which however refer to different areas of work. For example, steganography is often regarded as a form of covert channel [21-22]. Definition 6 is a definition used in such areas.

Definition 6: A covert channel is a parasitic communications channel that draws bandwidth from another channel in order to transmit information without the authorization or knowledge of the latter channel's designer, owner, or operator [22].

Unlike covert channels that exploit unintended mechanisms to transfer information, steganography hides information in legitimate text such as ordinary files and network

packets. Since the main interest of this area of work is the *covertness* (i.e., the *secrecy*) of the *communications* (not just the information being transferred), and because the term "information hiding" was not yet invented at that time [23], the term "covert channels" was also used in this area. In this dissertation, according to our definition of covert channels, steganography will not be discussed in the scope of covert channels but will be discussed as a form of information hiding technique.

The definition of covert channels in this dissertation also distinguishes side channels from covert channels. Although information leakage in covert channels and side channels may be based on the same physical mechanisms such as operation timings, side channel attacks assume no insiders and thus are unintentional information leakage. The targets of side channel attacks are mostly crypto ciphers which by no means would intentionally leak out information.

#### 2.1.2 Covert Channel Classification

In the literature, covert channels are often categorized into two types: covert *storage* channels and covert *timing* channels [18, 24-26]. Covert storage channels usually make use of objects not intended for data storage whereas covert timing channels exploit the temporal characteristics of events to transfer information. For example, TCSEC [18] adopted the following definitions:

Covert storage channels: covert channels that "would allow direct or indirect writing of a storage location by one process and the direct or indirect reading of it by another". Covert timing channels: covert channels that "would allow one process to signal information to another process by modulating its own use of system resources in such a way that the change in response time observed by the second process would provide information".

The file lock channel described in section 2.2 is a typical covert storage channel, which makes use of the file lock object to carry the information. The sender is able to "write" a bit to the file lock, though indirectly, and the receiver can "read" the file lock value. Many other mechanisms in operating systems can be exploited as well. For example, by allowing a process to detect whether a directory exists or not even though the process does not have enough security clearance to access the directory, an insider can send bits out by creating and removing a directory known by the receiver. Resource-exhaustion channels are another common class of storage channels. Based on the information bit to be sent, the insider can choose to use up, or not, the shared resources. The receiver then makes an allocation of the exploited resource and observes if the allocation fails, or not, to infer the bit. The CPU scheduling channel is a representative covert timing channel as the information is modulated over the observer's response time. Other shared resources can also be exploited to construct covert timing channels in a similar way. Indeed, almost all mechanisms that allow a process to impact the system performance can be exploited as timing channels [21].

In addition to those in standalone systems, covert channels exist in networks as well. Examples of covert storage channels in networks include those based on the pattern of the network packets' destination address, unused header bits and certain packet fields, and examples of covert timing channels include those based on packet rate, packet timing,

network protocols such as the Medium Access Control (MAC) protocol of wireless networks, etc. [27-34]. A survey of network covert channels can be found in [35].

The classification of covert channels as storage channels vs. timing channels is clear and helpful in covert channel analysis most of the time, and thus was widely accepted and used in the literature. However, researchers admitted that the difference between storage channels and timing channels is actually unclear [17, 23, 26] and there are covert channels that are hard to categorize. Below is an example:

#### **Example 3: the disk arm channel**

When servicing a sequence of disk access requests, the operating system often re-orders the requests to avoid unnecessary seek operations, i.e., the radial movements of the disk arm, which are very expensive in terms of time. Due to the similarity between the problem of scheduling a disk arm and that of scheduling an elevator in a tall building, the elevator algorithm is commonly used for disk access optimization, i.e., the disk arm keeps moving in the same direction until there are no more outstanding requests in that direction and then switches the direction. This allows a covert channel as described below. Assume that the inner-most cylinder is numbered 0 and the outer-most is numbered N. The receiving process R first initializes position of the disk arm to cylinder N/2 by requesting accesses to that cylinder. R relinquishes CPU after this access is completed. The sending process S can then encode a bit of information by accessing either cylinder 1 or N-1 to send a bit '0' or '1', respectively. To receive the bit sent by S, R issues two requests – one to cylinder 0 and the other to cylinder N, and observes the order of completion of the two requests. If the access to cylinder 0 completes first, it means that the disk arm's movement is  $N/2 \rightarrow 1 \rightarrow 0 \rightarrow N$ , indicating that S accessed cylinder 1 and thus a bit '0' is sent. If R's access to cylinder N completes first, the disk arm's movement is  $N/2 \rightarrow N-1 \rightarrow N \rightarrow 0$ , meaning that S accessed cylinder N-1 and thus a bit '1' is sent.

This channel was categorized as a storage channel by Karger [36]. His argument was that the disk arm is a storage object whose value is the position of the disk arm and there is no timing measurement involved in this channel. However, Wray, the second author of the paper, regarded the disk arm channel as a timing channel. He argued that the disk itself is a timer and observing the ordering of events is a kind of timing measurement [26]. In fact, the ambiguity of the difference between storage channels and timing channels is due to the non-rigorous definitions of the two types of channels. For example, the rigor in the definition of timing channels relies on the rigor in the definition of time, which however is ambiguous as illustrated in [26]. To the best knowledge of the author, this ambiguity is still unresolved.

### 2.1.3 Covert Channel Analysis

Dealing with the covert channel problem usually involves three steps: covert channel identification, capacity (or bandwidth) estimation, and covert channel handling. Covert channel identification attempts to find all, or as many as possible, covert channels in the system. Once identified, covert channels must be measured for their severity. A common metric is the channel capacity, or channel bandwidth, which measures how fast information can be sent over the channel. Depending on the needs, covert channels can be audited, mitigated, or eliminated.

#### 2.1.3.1 Identification

Covert channel identification requires the analysis of all or a subset of system documents, including high level system specifications, system reference manuals, implementation source code and hardware manuals. A common approach of covert channel analysis is flow analysis. Information flow can be derived from the documents by attaching information flow semantics to the statements of the specification or programming language. In a program, data dependency and control dependency lead to information flow. For example, both assignment statement "x:=y" and if-else statement "if (y==c)x:=a else x:=b;" causes information flow from variable y to variable x. Examples of more information flows in programming language statements can be found in [20, 37-38]. The derived flows are then checked with the flow policy which is a representation of the system security policy. Such a procedure can be automated for analysis over formal specifications and source code, which has been adopted in several tools, including the SRI Hierarchical Development Methodology (HDM) and Enhanced HDM (EHDM) tools [39-40], the Ida Flo tool [41] and the Gypsy tools [42-44]. Information flow analysis can be further augmented with more semantic components. In [45] Tsai presented a method based on the analysis of programming language semantics, kernel code and data structures, and the resolution of aliasing of kernel variables. Together with the information flow analysis, direct and indirect visibility and alterability of kernel variables are examined and potential covert storage channels are identified.

Information flow analysis methods shown above however are not suitable for specifications written with informal languages. In [15] Kemmerer proposed the Shared Resource Matrix (SRM) method which can be applied to both formal and informal specifications. The SRM approach requires the construction of a shared resource matrix from the specifications being analyzed. The matrix consists of visible/alterable shared resources and their attributes as columns and user-visible primitives as rows. Each entry of the matrix can be marked as either R or M if the corresponding primitive can reference (read) or modify (alter) the corresponding attribute. To identify indirect references to resource attributes, a transitive closure needs to be performed on the entries of the matrix. To detect potential covert channels, each column containing row entries with either an R or an M is analyzed since the resource attributes of these columns may be exploited for covert channels. A process that can alter an attribute can send information to a process that can read the same attribute, which may form a potential covert channel. Further analysis of the identified potential covert channels is then performed to determine if they are indeed exploitable. Some potential covert channels identified by the SRM method may be in parallel with an overt channel, or have the same process as both the sender and the receiver, or can only pass information that is already known by the receiver. Such channels are not real covert channels.

Based on similar information and procedures used in the SRM method, Porras and Kemmerer proposed the Covert Flow Tree (CFT) method [46] that allows the search for covert communication scenarios with a graphical tool. The dependency information is first analyzed, which identifies the resource attributes that should be further analyzed. The trees are then constructed for such attributes. The left branch of the tree is the series of operations caused by the sender to alter the attribute and the right branch is the operations that enable the receiver to perceive the modification. Potential channels are then analyzed as in the SRM method to determine if real covert channels exist.

Noninterference analysis is another popular covert channel analysis method, first introduced by Goguen and Meseguer [47]. It is based on the concept that "one user should not be aware of any activity of another user that he does not dominate" [48] and does not examine flows directly. By modeling the system as a state machine, a precise definition of noninterference can be expressed with the effects of the system's input history on a user's view of the system state and output. Loosely speaking, if user X does not interfere with user Y, deletion (or purge) of any or all X's inputs from the system's input history should not change Y's output. Formal definitions of noninterference can be found in [47, 49-50]. In practice, analyzing the entire history of the system inputs is infeasible, and the "Unwinding Theorem" solves this problem [51]. The "Unwinding Theorem" allows noninterference to be checked by examining the properties of the machine' state transition function, avoiding analysis of history traces. Noninterference analysis is advantageous for avoiding the discovery of false illegal flows. Its main drawback is that it requires the construction of the state machine and the selection of users' "view" functions that captures the system state visible to the user, which are nontrivial. Noninterference analysis was popular and has been applied to several systems including the SAT abstract model [52].

In summary, covert channel identification is a difficult problem which has not been completely solved despite all of the above work. On the one hand, the lack of formal specifications in real system designs disallows the use of the formal security-provable techniques, and at the same time analysis of informal specifications can not ensure security. Furthermore, it is really hard, if not impossible, to enumerate all possible information transfer mechanisms and include them into the system model. Under the "incomplete" system model, the ignored mechanisms can lead to covert channels even if the security of the system is theoretically proved.

#### 2.1.3.2 Capacity Estimation

The task of capacity estimation of a covert channel is to estimate the maximum attainable bit rate of information transfer over the channel. Millen [53] first connected information flow models to Shannon's communication theory [54] and introduced the notion of covert channel capacity as a measurement of the covert channel information rate.

Unlike in most traditional communication channels, the times required for sending different bit values in many covert channels are different and depend on the history of bit transmission. Such channel properties are better captured by a state machine model as proposed by Millen in [55]. Millen assumed that the channels are noiseless, without interruption from processes other than the sender and the receiver, and the time required for the synchronization between the sender and the receiver is negligible. Such assumptions are valid in the context of estimating the maximum information rate. With the help of information theory, capacity of the state machine channels can be calculated once the transition overheads are determined. Information theory based capacity analysis was also applied to various other types of channels. The related work include Moskowitz's work on the capacity of certain noisy timing channels [56], the simple timing channels [57], the Timed-Z channels [58], Kang's work on the pump [59-60], Gray's work on the bus-contention channel [61], Giles's work on channels based on packet timing [62], and Venkatraman's work on network channel capacities [63], etc.

The information rate of a covert channel can also be estimated with informal methods. In this dissertation, such estimation is referred to as bandwidth estimation rather than

capacity estimation although some past work used these two terms in an exchangeable manner. Capacity estimation gives the theoretical upper bound (which is tight) of the information rate whereas bandwidth estimation gives an approximation of the bound. Bandwidth estimation usually adopts simpler equations as an approximation for the rate calculation. Examples of such work can be found in [17, 64].

#### 2.1.3.3 Covert Channel Handling

The purpose of covert channel handling is to minimize the damage of covert channels to system security. The ultimately secure way to deal with covert channels is to eliminate them. Some covert channels can be closed by redesigning the system. For example, the file lock channel can be blocked by disallowing a user to check the lock status of a file that he is not entitled to access. However, handling all covert channels in a system via channel elimination is practically impossible. For example, closing covert channels based on shared resources would essentially require strict resource partitioning or no resource sharing at all. Such an approach may be applicable to small system modules without sacrificing system usability and performance, but applying it to the whole system would normally impose too many restrictions on the system design and eventually lead to unusable systems.

Another covert channel handling strategy is through deterrence. The main deterrence method is channel auditing. If a known covert channel involves operations that are normally infrequently used and has low capacity, handling it via auditing can be a good choice. It is easy for the auditing system to detect the use of such a channel with reasonable expenses on recording, and before the channel use is detected only a tolerable amount of information can be leaked out. Channel auditing however has several fundamental problems. Not all covert channels are suitable for auditing, and some of them are simply undetectable. The use of a covert channel is usually detected afterwards, sometime long after the occurrence and the damage has been done. The analysis of audit data is nontrivial and could be very time consuming. More details about the problems of channel auditing can be found in [65].

The third method of covert channel handling is based on capacity reduction. Such a method does not eliminate the covert channel completely, but makes it much slower. One class of the work aimed to reduce capacities of timing channels by playing tricks with time. Popek and Kline proposed to restrict each process to see only virtual time, which depends solely on its own activity [66]. By making the time of each process less correlated to each other, the capacities of timing channels between these processes are reduced. Hu proposed to use "fuzzy time" [25] in the system, which makes all timing sources visible to the processes noisy. Giles et al. proposed the timing jammer to mitigate the packet timing channels [62, 67]. Noisy timing measurement would generally lead to lower capacity of most timing channels. Another approach for reducing covert channel capacity is to slow things down such that given the same amount of time, less information can be transferred. The most straight forward implementation is to slow everyone down, e.g., by adding delay to every system call in a system [23]. In [68] Hu proposed the lattice scheduling technique which makes use of the secrecy class attributes of processes to make decisions. The lattice scheduler reduces the frequency of transitions between processes that could be the two ends of the covert channel and slows down the transmission procedure. Resource partitioning can also be used to reduce covert channel capacity. Gray proposed probabilistic partitioning to mitigate the bus-contention channel [61]. Reducing covert channel capacity is also an interesting topic in the design of legitimate communication channels between security domains, e.g., from the low security level to the high security level. To ensure reliable communications, feedback mechanisms are usually needed to send back reception acknowledgements to the sender who is at the low security level, which leads to covert channels. To reduce the capacity of such covert channels, the pump and its variants were proposed [59-60, 69-70]. By placing a buffer between Low and High, the acknowledgements from High to Low are decoupled into two separate ACKs, one from the buffer to Low and the other from High to the buffer. By properly controlling the ACK times, the capacity of the covert timing channel can be reduced without compromising the reliability and performance of the legitimate communication channels.

The covert channel problem in general is a hard problem. It is believed impossible to make any realistic systems free of covert channels. There is always a trade-off between the level of security and the performance, usability, cost, etc.

#### 2.2 Side Channel Attacks

#### 2.2.1 Overview

Side channel attacks are a special class of attacks that are based on indirect information leakage due to a systems' physical implementation. During the operation of a system, the variation of the system's power supply current, operation timing, electromagnetic radiation and/or acoustic emission can all carry information – often referred to as side channel information – which reveals the system's internal states and the data being processed. Although theoretically side channel information can be exploited to attack all kinds of systems, in practice the targets of the attacks are mostly implementations of cryptosystems, particularly simple cryptographic devices such as smart cards.

Side-channel cryptanalysis is different from classical cryptanalysis although they both aim to break cryptosystems. Classical cryptanalysis views the target cryptosystem as an abstract mathematical object and attacks the weakness of the mathematical composition itself, whereas side-channel cryptanalysis views the target as a particular physical realization and attacks the system physically rather than mathematically. Although side-channel cryptanalysis is much less general than classical cryptanalysis due to its implementation-specific nature, it is often much more powerful. Classical cryptanalysis typically requires a huge amount of computation and is only able to shrink the search space for the secrets. If the cipher is mathematically strong, classical cryptanalysis may be practically ineffective. In contrast, side-channel cryptanalysis often can recover more secret information – sometimes the full crypto key – in a much shorter time. It can be very effective even in attacking mathematically strong ciphers.

#### 2.2.2 Classification of Side Channel Attacks

In the literature, side channel attacks are usually classified in two different ways.

Passive vs. active: In passive attacks, the attacker does not interfere with the target system and only observes the system's normal behavior. In active attacks, the attacker

tries to tamper with the system's normal operations, e.g., by introducing faults into the computation, and deduces useful information from the system's responses.

Invasive vs. non-invasive: Invasive attacks usually involve physical deconstruction of some parts of the target system, e.g., depackaging a chip, to gain access to some internal components such as an internal data bus. Non-invasive attacks only exploit externally available information such as power supply current, operation timing etc. In [71], Skorobogatov et al. introduced a new type of attacks – the semi-invasive attacks. These attacks require depackaging the chip to gain access to the chip surface, but do not tamper with the chip further to probe internal components.

Note that the above two classification methods are orthogonal. For example, a passive attack may require depackaging a chip to gain access to the necessary information sources, and an active attack does not always imply an invasive attack – faults can be introduced with nondestructive methods, e.g., by heating the chip.

Although invasive attacks often allow the attacker to gain access to more information which makes the attack more powerful, in practice non-invasive attacks seem to receive more research and engineering effort due to economic reasons. Invasive attacks often require special equipment such as a scanning electron microscope or a probing station which are expensive and usually not available for individuals. Non-invasive attacks do not have this requirement and can be adopted more widely.

#### 2.2.3 Representative Attacks

Side channel attacks are extremely implementation-specific and this review does not attempt to list all of them. Below we briefly introduce representative attacks in each category and give references to other related work.

#### 2.2.3.1 Power analysis attacks

The power consumption of a cryptographic device often carries much information about the operation taking place and the data being processed in the device. In [72] Kocher et al. first presented attacks based on power analysis – referred to as simple power analysis (SPA) and differential power analysis (DPA).

The power measurements involved in power analysis are usually referred to as traces. A trace consists of a set of measurement samples, e.g., the power supply current, during a cryptographic operation. Due to the physical characteristics of the device, the device's internal states and the operations taking place in the device are transformed into the variation of the power consumption, which is recorded in the traces and can be recovered directly or statistically.

Simple Power Analysis (SPA): SPA refers to the technique that analyzes variations in the power traces that are directly distinguishable. Such large-scale variations are usually due to the execution of different operations. In implementations with software running on processors, different instruction sequences exhibit different power consumption profiles. In pure hardware implementations, different function modules consume different amount of power. In real attacks, SPA can identify operations with unique properties, e.g., round operations in ciphers like DES and AES – they cause repetitive patterns in power traces.

A more significant application of SPA is to identify conditional branches, which exhibit different SPA characteristics when executing different paths. In some RSA implementations, the conditional branches in exponentiation operations are controlled by the secret key bits. Finding out the branching direction would directly lead to the recovery of the secret key bit. Identifying conditional branches was also adopted in SPA to recover information from the DES key schedule computation, DES permutations, and various string or memory comparison operations [72].

Differential Power Analysis (DPA): DPA aims to recover information from subtle variations in the power traces that SPA can not exploit and thus is more powerful. In particular, the power variations correlated to a device's internal states are usually very small and overshadowed by the large-scale signals and measurement noise. Statistical techniques are employed in DPA to amplify the weak signal of interest and remove the effects of noise as well as other unrelated signals. Although the exact form of DPA is attack-specific, the underlying ideas are similar. In a typical DPA, the attacker first selects an internal state to exploit – often an intermediate result of the cryptographic computation that depends only on the plaintext or ciphertext, and a small part of the secret key (meaning a small search space). The effects of the selected state on power consumption therefore carry information about the secret key. Multiple power traces are normally needed to provide enough samples for statistical analysis. The key recovery procedure typically involves tests of a small number of hypotheses on the secret key values in the search space using the power measurement samples. Below is an example.

Let  $S(C,"b",K_s)$  denote the function – often referred to as the *selection function* – that describes the relation between the selected state b (e.g., a binary bit), the system input or output C (e.g., the plaintext or ciphertext), and the secret  $K_s$  (e.g., a byte of the secret key). The outcome of the selection function  $S(C,"b",K_s)$  is the value of the state b given the values of C and  $K_s$ . In DPA, the attacker knows the C value for each trace T. He guesses possible values of  $K_s$  in the search space and tests if the hypotheses are true. To test a hypothesis, each power trace is classified as a 1-trace or a 0-trace based on the outcome the selection function given the trace's C value and the guessed value of  $K_s$ . A 1-trace has a corresponding b=1 and a 0-trace has a corresponding b=0. The hypothesis can be tested by computing the difference between the averages of 1-traces and 0-traces:

$$\Delta T = \frac{1}{M1} \sum_{i=1}^{M1} T_i \Big|_{b=1} - \frac{1}{M0} \sum_{i=1}^{M0} T_i \Big|_{b=0}$$

(2.1)

where M1 and M0 are the numbers of 1-traces and 0-traces, respectively. For a correct guess of the  $K_s$  value, the classification of 1-traces and 0-traces is correct and the mean computations in (2.1) average out the noise in 1-traces and 0-traces while maintaining the bias caused by b. The subtraction then removes the common signals that is unrelated to b.  $\Delta T$  therefore measures the power variation due to different values of b. If the hypothesis is wrong, the traces are incorrectly classified and the computed  $\Delta T$  is roughly zero. The attacker tests hypotheses on all possible key values in the search space. The key value with a corresponding  $\Delta T$  that is sufficiently different from zero is likely the correct guess.

More advanced power analysis techniques were also available. An important improvement of DPA is high-order DPA [73-75]. Instead of assuming that at some point of the computation the intermediate state value is correlated to the power consumption as in classical DPA, high-order DPA considers effects of the state at multiple points in the

power consumption curve. The resulting differential function – the equation (2.1) in the case of classical DPA – has a high-order form. High-order DPA is able to break countermeasures that defeat classical DPA [76]. Another important improvement on power analysis is the template attack [77-78]. Template attacks rely on precise modeling of noise, with which the attacker is able to fully extract information from a *single* sample. Template attacks however require the attacker to possess an experimental device identical to the target system on which he can do experiments of his choice.

Power analysis has been demonstrated very effective in attacking various implementations of almost all major cryptosystems. Numerous reports were published on attacks on software as well as hardware implementations of DES [72, 79-83], AES [84-91], RSA [92-95], Elliptic Curve Cryptosystems (ECC) [96-100], RC4 [77], IDEA, RC6 and HMAC [101]. A comprehensive review of power analysis can be found in [102].

#### 2.2.3.2 Timing analysis attacks

Operation timing is another important source of side channel information. The variations in execution time can be the result of multiple factors: the operation's inherent computation complexity, software implementation issues such as branches and conditional execution of operations, and hardware dependent effects such as cache misses and variable branching penalty.

The idea of timing analysis of cryptosystems was first introduced by Kocher in [103] where he analyzed implementations of Diffie-Hellman, RSA and RSS. A timing attack was then practically implemented against an RSA implementation with Montgomery algorithm [104]. The attack was further improved in [105-106] and was able to recover a 512-bit secret key with 5000~10000 timing measurements. Timing analysis was also applied to RSA implementations that use Chinese Reminder Theorem (CRT). The resulting attack was very powerful – a 1024-bit secret key can be recovered using about 370 time measurements [107]. In addition to attacks targeted at local machines, timing analysis even allows attacks over networks. In [108], a remote attack against the OpenSSL implementation of RSA was demonstrated practical, despite the high noise level in real world networks. This work was further improved in [109]. Timing attacks were also applied to block ciphers such as AES [106].

Most of the early work on timing analysis were based on a *black-box* model, i.e., only externally available signals (normally the running time of the entire cryptographic operation) are accessible to the attacker. This is particularly true in attacks on embedded devices such as smart cards where the timings of the internal sub-operations are normally unavailable. Timing analysis attacks under such a model therefore rely on statistical analysis and require a considerable number of time measurements. The recent cache attacks, however, have demonstrated that information leakage in processor caches enables richer forms of attacks based on both *black-box* analysis and *white-box* analysis. The attacks are generally effective – almost all processors with caches are vulnerable, and can be used to attack embedded devices as well as general purpose systems. Cache attacks have received significant interest due to their wide impact.

In the literature, Page first described theoretical attacks based on information leakage in caches and categorized the attacks into two types: trace-driven attacks vs. time-driven attacks [110]. The attacker in trace-driven attacks is able to detect the outcome of each victim's memory reference in terms of hit or miss whereas in time-driven attacks, the attacker can only see an aggregated profile, e.g., the total number of hits or misses.

Although Page's work is not specifically in the context of timing analysis, most existing cache attacks employ timing analysis due to the convenient timing measurements with the high accuracy timers widely available in modern processors. Also, some processor features such as Simultaneous Multi-Threading (SMT) allow an attacker to run in parallel with the victim on the same chip and observe the victim's memory references in real time which exposes information about the internal sub-operations of the target cryptosystem. In addition to the trace-driven and time-driven types of attacks, a cache attack can also be classified as an access-driven attack [111]. The attacker in an access-driven attack is able to learn not only the cache's hit/miss behavior but also which cache lines/sets are touched, individually or in an aggregated manner.

The first practical cache attack was implemented by T sunoo et al. [112-113] in 2002 and 2003. The attack exploits the cache collisions in DES code and was a timedriven attack. In 2005, Bernstein showed the vulnerability of software AES implementations due to evictions of AES table entries in the cache and presented a timedriven attack that was able to recover a large portion of the key (the exact number of key bits that are recoverable depends on the cache configuration of the target system) [114]. This attack was further improved in [115] by exploiting the second round operation of AES – in addition to the first round operation, and was able to recover the full key. Bonneau et al. [116] proposed another time-driven attack that requires less timing measurements than in Bernstein's attack. This attack relies on cache collisions - cache hits due to accesses to the same AES table entry – rather than cache evictions of AES table entries. In [117], Aciicmez et al. pointed out the infeasibility of the existing cache attacks as remote attacks and proposed a real remote attack. A significant amount of timing measurements however are required. In addition to time-driven attacks, Osvik et al. also described several variants of cache attacks against AES in [118] and [119], in which the attacker is able to detect individual internal operations such as AES table lookups by making use of Simultaneous Multi-Threading (SMT). The attacker runs simultaneously with the victim process on the same chip where the cache is shared. Due to the cache line evictions caused by the victim, the attacker is able to learn which cache lines/sets are touched by individual memory references of the victim. The resulting attacks are very powerful. In [120], Neve et al. improved the attacks by making use of the final round operation of AES and making the use of SMT not necessary. Similar techniques were also adopted by Percival in his attack against RSA [121]. The full 1024-bit secret key can be recovered in a single encryption.